# **AN-8035**

# Design Consideration for Boundary Conduction Mode Power Factor Correction (PFC) Using FAN7930

#### 1. Introduction

This application note presents practical step-by-step design considerations for a Boundary-Conduction-Mode (BCM) Power-Factor-Correction (PFC) converter employing Fairchild PFC controller, FAN7930. It includes designing the inductor and Zero-Current-Detection (ZCD) circuit, selecting the components, and closing the control loop. The design procedure is verified through an experimental 200W prototype converter.

Unlike the Continuous Conduction Mode (CCM) technique often used at this power level, BCM offers inherent zero-current switching of the boost diodes (no reverse-recovery losses), which permits the use of less expensive diodes without sacrificing efficiency.

FAN7930 has a PFC-ready pin to acknowledge when PFC output voltage reaches stable operation range. This signal can be used as the  $V_{\rm CC}$  trigger signal for another power stage controller after PFC stage or be transferred to the secondary side to synchronize the operation with PFC voltage condition. This simplifies the external circuit

around the PFC controller and saves total BOM cost. The internal proprietary logic for detecting input voltage greatly improves the stability of PFC operation. Together with the maximum switching frequency clamping at 300kHz, FAN7930 can limit inductor current within predesigned value at one or two cycles of the AC-inputabsent test to simulate a sudden blackout. Due to the startup-without-overshoot design, audible noise from repetitive OVP triggering is eliminated. Protection functions include output over-voltage, over-current, openfeedback, and under-voltage lockout.

An Excel<sup>®</sup>-based design tool is available with this application note and the design result is shown with the calculation results as an example.

Visit <a href="http://www.fairchildsemi.com/design\_tools/">http://www.fairchildsemi.com/design\_tools/</a> to download the design tool.

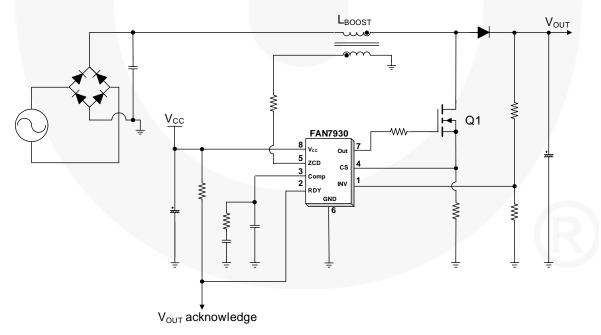

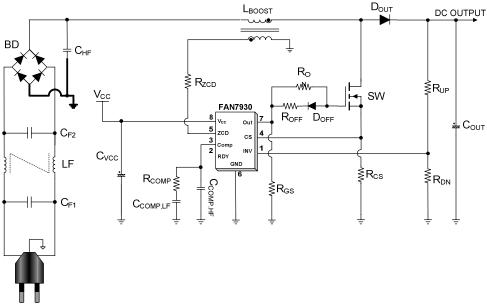

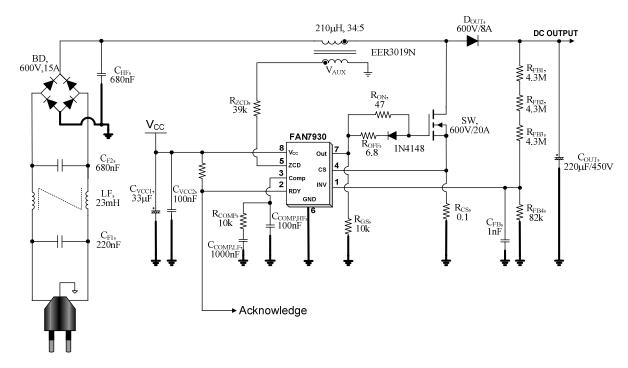

Figure 1. Typical Application Circuit

Excel<sup>®</sup> is a registered trademark of Microsoft Corporation.

# 2. Operation Principle of BCM Boost PFC Converter

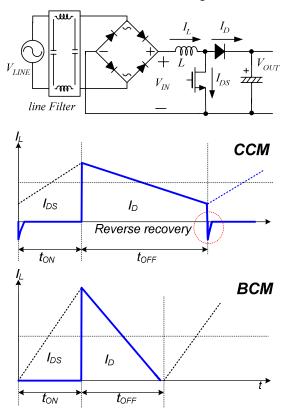

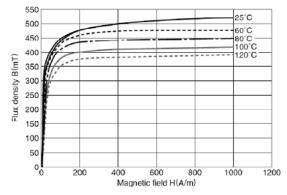

The most widely used operation modes for the boost converter are continuous conduction mode (CCM) and boundary conduction mode (BCM). These two descriptive names refer to the current flowing through the energy storage inductor of the boost converter, as depicted in Figure 2. As the names indicate, the inductor current in CCM is continuous; while in BCM, the new switching period is initiated when the inductor current returns to zero, which is at the boundary of continuous conduction and discontinuous conduction operations. Even though the BCM operation has higher RMS current in the inductor and switching devices, it allows better switching condition for the MOSFET and the diode. As shown in Figure 2, the diode reverse recovery is eliminated and a fast-recovery diode is not needed. The MOSFET is also turned on with zero current, which reduces the switching loss.

Figure 2. CCM vs. BCM Control

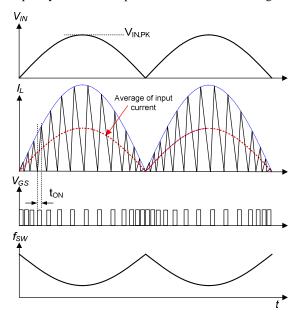

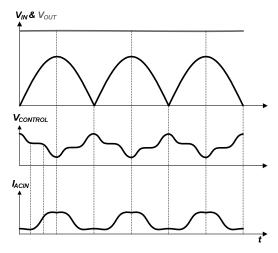

The fundamental idea of BCM PFC is that the inductor current starts from zero in each switching period, as shown in Figure 3. When the power transistor of the boost converter is turned on for a fixed time, the peak inductor current is proportional to the input voltage. Since the current waveform is triangular; the average value in each switching period is proportional to the input voltage. In a sinusoidal input voltage, the input current of the converter follows the input voltage waveform with very high accuracy and draws a sinusoidal input current from the source. This behavior makes the boost converter in BCM operation an ideal candidate for power factor correction.

A by-product of BCM is that the boost converter runs with variable switching frequency that depends primarily on the selected output voltage, the instantaneous value of the input voltage, the boost inductor value, and the output power delivered to the load. The operating frequency changes as the input current follows the sinusoidal input voltage waveform, as shown in Figure 3. The lowest frequency occurs at the peak of sinusoidal line voltage.

Figure 3. Operation Waveforms of BCM PFC

The voltage-second balance equation for the inductor is:

$$V_{IN}(t) \cdot t_{ON} = (V_{OUT} - V_{IN}(t)) \cdot t_{OFF} \tag{1}$$

where  $V_{\text{IN}(t)}$  is the rectified line voltage and  $V_{\text{OUT}}$  is the output voltage.

The switching frequency of BCM boost PFC converter is:

$$f_{SW} = \frac{1}{t_{ON} + t_{OFF}} = \frac{1}{t_{ON}} \cdot \frac{V_{OUT} - V_{IN}(t)}{V_{OUT}}$$

$$= \frac{1}{t_{ON}} \cdot \frac{V_{OUT} - V_{IN,PK} \cdot \left| sin(2\pi \cdot f_{LINE} \cdot t) \right|}{V_{OUT}}$$

(2)

where  $V_{\text{IN},PK}$  is the amplitude of the line voltage and  $f_{\text{LINE}}$  is the line frequency.

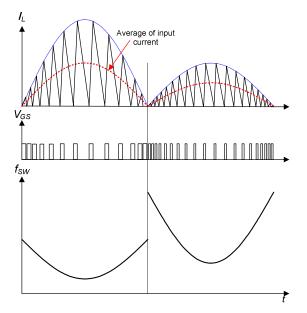

Figure 4 shows how the MOSFET on time and switching frequency changes as output power decreases. When the load decreases, as shown in the right side of Figure 4, the peak inductor current diminishes with reduced MOSFET on time and, therefore, the switching frequency increases. Since this can cause severe switching losses at light-load condition and too-high switching frequency operation may occur at startup, the maximum switching frequency of FAN7930 is limited to 300kHz.

Figure 4. Frequency Variation of BCM PFC

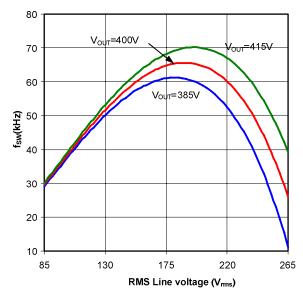

Since the design of the filter and inductor for a BCM PFC converter with variable switching frequency should be at minimum frequency condition, it is worthwhile to examine how the minimum frequency of BCM PFC converter changes with operating conditions.

Figure 5 shows the minimum switching frequency, which occurs at the peak of line voltage as a function of the RMS line voltage for three output voltage settings. It is interesting that, depending on where the output voltage is set, the minimum switching frequency may occur at the minimum or at the maximum line voltage. When the output voltage is approximately 405V, the minimum switching frequency is the same for both low line (85V $_{\rm AC}$ ) and high line (265V $_{\rm AC}$ ).

Figure 5. Minimum Switching Frequency vs. RMS Line Voltage (L = 390µH, P<sub>OUT</sub> = 200W)

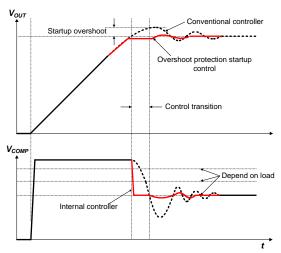

# 3. Startup without Overshoot and AC-Absent Detection

Feedback control speed of the PFC is typically quite slow. Due to the slow response, there is a gap between output voltage and feedback control. That is why Over-Voltage Protection (OVP) is critical at the PFC controller. Voltage dip caused by fast load change from light to heavy is diminished by a large bulk capacitor. OVP is easily triggered at startup. Switching starting and stopping by OVP at startup may cause audible noise and can increase voltage stress at startup, which may be higher than normal operation. This operation is improved when soft-start time is very long. However, too-long startup time raises the time needed for the output voltage to reach the rated value, especially at light load. FAN7930 includes a startup without overshoot feature. During startup, the feedback loop is controlled by an internal proportional gain controller and, when the output voltage reaches the vicinity of the rated value, changed to the external compensator after an internally fixed transition time described in the Figure 6. In short, an internal proportional gain controller prevents overshoot at startup; external conventional compensator takes over after startup.

Figure 6. Startup Without Overshoot

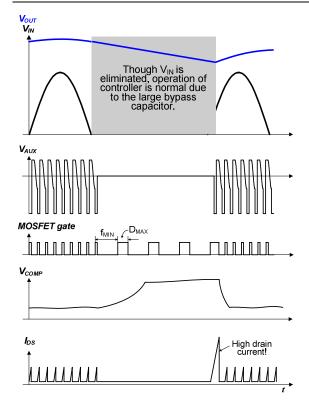

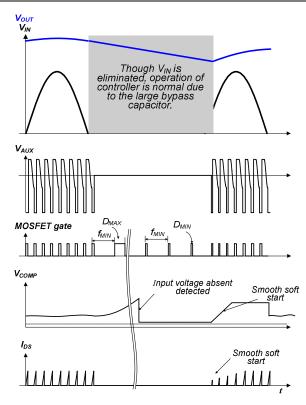

FAN7930 eliminates AC input voltage detection to save the power loss caused by an input-voltage-sensing resistor array and to optimize THD. Therefore, no information about input voltage is available at the internal controller. In many cases, the  $V_{CC}$  of PFC controller is supplied by an independent power source, like standby power, so when the electric power is suddenly interrupted during one or two AC line periods, V<sub>CC</sub> is still alive during that time and PFC output voltage drops. Accordingly, the control loop tries to compensate output voltage drop and control voltage reaches its maximum. When AC line input voltage is live, control voltage allows high switching current and creates stress on the MOSFET and diode. To protect against this, FAN7930 checks if the input AC voltage exists. Once controller verifies that the input voltage does not exist, soft-start is reset and waits until AC input voltage is applied again. Soft-start manages the turn-on time for smooth operation after detecting that the AC voltage is live and results in less voltage and current stress during startup.

Figure 7. AC-Off Operation without AC-Absent Detection Circuit

Figure 8. AC-Off Operation with AC-Absent Detection Circuit

# 4. Design Considerations

In this section, a design procedure is presented using the schematic in Figure 9 as a reference. A 200W PFC application with universal input range is selected as a design example. The design specifications are:

- Line Voltage Range: 90~265V<sub>AC</sub> (Universal Input), 50Hz

- Nominal Output Voltage and Current: 400V/0.5A (200W)

- Hold-up Time Requirement: Output Voltage Should Not Drop Below 330V During One Line Cycle

- Output Voltage Ripple: Less than 8V<sub>PP</sub>

- Minimum Switching Frequency: Higher than 40kHz

- Control Bandwidth: 5~15Hz

- V<sub>CC</sub> supplied from auxiliary power supply.

Figure 9. Reference Circuit for Design Example of BCM Boost PFC

#### [STEP-1] Define System Specifications

- Line Frequency Range ( $V_{LINE,MIN}$  and  $V_{LINE,MAX}$ )

- Line Frequency  $(f_{LINE})$

- Output-Voltage ( $V_{OUT}$ )

- Output Load Current (*I<sub>OUT</sub>*)

- Output Power  $(P_{OUT} = V_{OUT} \times I_{OUT})$

- Estimated Efficiency (n)

To calculate the maximum input power, it is necessary to estimate the power conversion efficiency. At universal input range, efficiency is recommended at 0.9; 0.93~0.95 is recommended when input voltage is high.

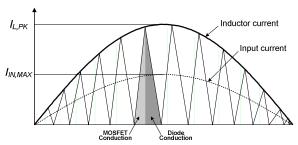

When input voltage is set at the minimum, input current becomes the maximum to deliver the same power compared at high line. Maximum boost inductor current can be detected at the minimum line voltage and at its peak. Inductor current can be divided into two categories; one is rising current when MOSFET is on and the other is output diode current when MOSFET is off, as shown in Figure 10.

Figure 10. Inductor and Input Current

Because switching frequency is much higher than line frequency, input current can be assumed to be constant during a switching period, as shown in Figure 11.

Figure 11. Inductor and Input Current

With the estimated efficiency, Figure 10 and Figure 11 inductor current peak  $(I_{L,PK})$ , maximum input current  $(I_{IN,MAX})$ , and input RMS (Root Mean Square) current  $(I_{IN,MAXRMS})$  are given as:

$$I_{L,PK} = \frac{4 \cdot P_{OUT}}{\eta \cdot \sqrt{2} \cdot V_{LINE \cdot MIN}} [A]$$

(3)

$$I_{IN,MAX} = I_{L,PK}/2 [A]$$

(4)

$$I_{IN,MAXRMS} = I_{IN,MAX} / \sqrt{2} [A]$$

(5)

(Design Example) Input voltage range is universal input, output load is 500mA, and estimated efficiency is selected as 0.9.

$$V_{LINE,MIN} = 90V_{AC}, \ V_{LINE,MAX} = 265V_{AC}$$

$$f_{LINE} = 50Hz$$

$$V_{OUT} = 400V, \ I_{OUT} = 500mA$$

$$\eta = 0.9$$

$$I_{L,PK} = \frac{4 \cdot P_{OUT}}{\eta \cdot \sqrt{2} \cdot V_{LINE,MIN}} = \frac{4 \cdot 400V \cdot 0.5A}{0.9 \cdot \sqrt{2} \cdot 90} = 6.984A$$

$$I_{IN,MAX} = \frac{I_{L,PK}}{2} = \frac{6.984A}{2} = 3.492A$$

$$I_{IN,MAXRMS} = \frac{I_{IN,MAX}}{\sqrt{2}} = \frac{3.492A}{\sqrt{2}} = 2.469A$$

$$\frac{1.\text{Define System Specifications}}{\text{Minimum Line Voltage }(V_{\text{LINE,MIN}})} = \frac{90}{4000} V_{AC}$$

$$V_{AC} = V_{AC}$$

$$V_$$

#### **ISTEP-21 Boost Inductor Design**

Maximum Peak Inductor Current (ILPK)

Maximum RMS Input Current (IIN, MAXRMS)

Max Peak Inductor Current@V<sub>LINE.MAX</sub> (I<sub>L.PK</sub>@V<sub>LINE.MAX</sub>)

Maximum Input Current@V<sub>LINE,MAX</sub> (I<sub>IN,MAX</sub>@V<sub>LINE,MAX</sub>)

Max RMS Input Current@VLINE,MAX (IIN,MAXRMS@VLINE,MAX)

Maximum Input Current (IIN,MAX)

Input Power (PIN)

The boost inductor value is determined by the output power and the minimum switching frequency. The minimum switching frequency must be higher than the maximum audible frequency band of 20kHz. Minimum frequency near 20kHz can decrease switching loss with the cost of increased inductor size and line filter size. Toohigh minimum frequency may increase the switching loss and make the system respond to noise. Selecting in the range of about 30~60kHz is a common choice; 40~50kHz is recommended with FAN7930.

The minimum switching frequency may appear at minimum input voltage or maximum input voltage, depending on the output voltage level. When PFC output voltage is less than 405V, minimum switching appears at the maximum input voltage, according to Fairchild application note AN-6086. The inductance is obtained using the minimum switching frequency:

$$L = \frac{\eta \cdot \left(\sqrt{2}V_{LINE}\right)^{2}}{4 \cdot f_{SW,MIN} \cdot P_{OUT} \cdot \left(1 + \frac{\sqrt{2}V_{LINE}}{V_{OUT} - \sqrt{2}V_{LINE}}\right)} [H]$$

(6)

where L is boost inductance and  $f_{\text{SW,MIN}}$  is the minimum switching frequency.

222.22 W

6.984

3.492

2.469

2.372

1.186

The maximum on time needed to carry peak inductor current is calculated as:

$$t_{ON,MAX} = L \cdot \frac{I_{L,PK}}{\sqrt{2} \cdot V_{LINE,MIN}} [s]$$

(7)

Once inductance and the maximum inductor current are calculated, the number of turns of the boost inductor should be determined considering the core saturation. The minimum number of turns is given as:

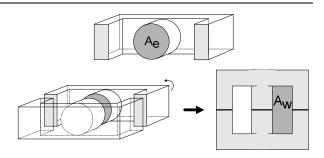

$$N_{BOOST} \ge \frac{I_{L,PK} \cdot L[\mu H]}{A_{P}[mm^2] \cdot \Delta B} [Turns]$$

(8)

where  $A_e$  is the cross-sectional area of core and  $\Delta B$  is the maximum flux swing of the core in Tesla.  $\Delta B$  should be set below the saturation flux density.

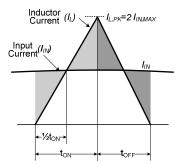

Figure 12 shows the typical B-H characteristics of ferrite core from TDK (PC45). Since the saturation flux density ( $\Delta B$ ) decreases as the temperature increases, the high temperature characteristics should be considered.

RMS inductor current ( $I_{L,RMS}$ ) and current density of the coil ( $I_{L,DENSITY}$ ) can be given as:

$$I_{L,RMS} = \frac{I_{L,PK}}{\sqrt{6}} [A]$$

(9)

$$I_{L,DENSITY} = \frac{I_{L,RMS}}{\pi \cdot \left(\frac{d_{wire}}{2}\right)^2 \cdot N_{wire}} [A/mm^2]$$

(10)

where  $d_{WIRE}$  is the diameter of winding wire and  $N_{WIRE}$  is the number of strands of winding wire.

When selecting wire diameter and strands; current density, window area ( $A_W$ , refer to Figure 13) of selected core, and fill factor need to be considered. Winding sequence of the boost inductor is relatively simple compared to a DC-DC converter, so fill factor can be assumed about  $0.2 \sim 0.3$ .

Layers cause the skin effect and proximity effect in the coil, so real current density may be higher than expected.

Figure 12. Typical B-H Curves of Ferrite Core

Figure 13.  $A_e$  and  $A_w$

**(Design Example)** Since the output voltage is 400V, the minimum frequency occurs at high-line ( $265V_{AC}$ ) and full-load condition. Assuming the efficiency is 90% and selecting the minimum frequency as 50kHz, the inductor value is obtained as:

$$L = \frac{\eta \cdot \left(\sqrt{2}V_{LINE}\right)^{2}}{4 \cdot f_{SW,MIN} \cdot P_{OUT} \cdot \left(1 + \frac{\sqrt{2}V_{LINE}}{V_{OUT} - \sqrt{2}V_{LINE}}\right)}$$

$$= \frac{0.9 \cdot \left(\sqrt{2} \times 265\right)^{2}}{4 \cdot 50 \cdot 10^{3} \cdot 200 \cdot \left(1 + \frac{\sqrt{2} \cdot 265}{400 - \sqrt{2} \cdot 265}\right)} = 199.4[\mu H]$$

Assuming EER3019N core (PL-7,  $A_e=137$ mm<sup>2</sup>) is used and setting  $\Delta B$  as 0.3T, the primary winding should be:

$$N_{BOOST} \ge \frac{I_{L,PK} \cdot L[\mu H]}{A_{P}[mm^2] \cdot \Delta B} = \frac{6.984 \cdot 209}{137 \cdot 0.3} = 34[T]$$

The number of turns  $(N_{BOOST})$  of the boost inductor is determined as 34 turns.

When 0.10mm diameter and 50-strand wire is used, RMS current of inductor coil and current density are:

$$\begin{split} I_{L,RMS} &= \frac{I_{L,PK}}{\sqrt{6}} = \frac{6.984}{\sqrt{6}} = 2.85 [A] \\ I_{L,DENSITY} &= \frac{I_{LRMS}}{\pi \cdot \left(\frac{d_{wire}}{2}\right)^2 \cdot N_{wire}} = \frac{2.85}{\pi \cdot (0.1/2)^2 \cdot 50} = 7.3 \ [A/mm^2] \end{split}$$

| Minimum Switching Frequency (f <sub>SW,MIN</sub> )            | 50.0         | kHz |

|---------------------------------------------------------------|--------------|-----|

| Needed Boost Inductor @Low Line                               | 248.5        | μΗ  |

| Needed Boost Inductor @High Line                              | 199.4        | μΗ  |

| Boost Inductor (L)                                            | <u>199.4</u> | μH  |

| Maximum ON Time @V <sub>LINE,MIN</sub> (t <sub>ON,MAX</sub> ) | <u>10.9</u>  | μs  |

| Maximum OFF Time @V <sub>LINE,MIN,PK</sub>                    | 5.1          | μs  |

| Maximum ON time @V <sub>LINE,MAX</sub>                        | 1.3          | μs  |

| Maximum OFF Time @V <sub>LINE,MAX,PK</sub>                    | 18.7         | μs  |

| Core Selection                                                |              |     |

| Saturation Flux Density (B <sub>sat</sub> )                   | 0.30         | Tes |

| Effective Cross-Sectional Area of Selected Core (Ae)          | 137.0        | mm  |

| Winding Area of Selected Bobbin (A <sub>w</sub> )             | 110.0        | mm  |

| Fill Factor                                                   | 0.25         | *   |

| Winding Strands                                               | 50           | *   |

| Winding Diameter                                              | 0.10         | mm  |

| Minimum Number of Turns (N <sub>BOOST</sub> )                 | <u>34</u>    | Tur |

| Air gap Length                                                | <u>1.0</u>   | mm  |

| Maximum Current Density of Coil (I <sub>L,DENSITY</sub> )     | <u>7.3</u>   | A/n |

| Necessary Window Area (A <sub>W</sub> )                       | 53.4         | mm  |

#### [STEP-3] Inductor Auxiliary Winding Design

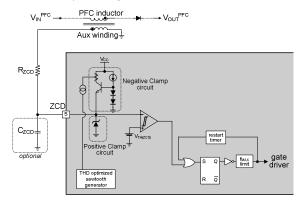

Figure 14 shows the application circuit of nearby ZCD pin from auxiliary winding.

Figure 14. Application Circuit of ZCD Pin

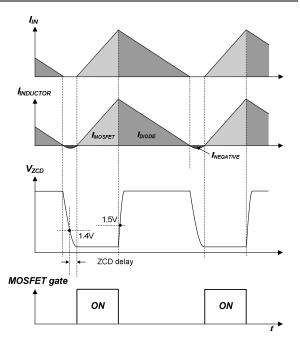

The first role of ZCD winding is detecting the zero-current point of the boost inductor. Once the boost inductor current becomes zero, the effective capacitor shown at the MOSFET drain pin  $(C_{\it eff})$  and the boost inductor resonate together. To minimize the constant turn-on time deterioration and turn-on loss, the gate is turned on again when the drain source voltage of the MOSFET  $(V_{\it DS})$  reaches the valley point shown in Figure 15. When input voltage is lower than half of the boosted output voltage, zero voltage switching (ZVS) is possible if MOSFET turn-on is triggered at valley point.

Figure 15. ZCD Detection Waveforms

Auxiliary winding must give enough energy to trigger ZCD threshold to detect zero current. Minimum auxiliary winding turns are given as:

$$N_{AUX} \ge \frac{1.5V \cdot N_{BOOST}}{V_{OUT} - \sqrt{2}V_{LINEMAX}} [Turns]$$

(11)

where 1.5V is the positive threshold of the ZCD pin.

To guarantee stable operation, auxiliary winding turns are recommended to add 2~3 turns to the calculation result of Equation (11). However, too many auxiliary winding turns raise the negative clamping loss at high line and positive clamping loss at low line.

(**Design Example**) 34 turns are selected as boost inductor turns and auxiliary winding turns are calculated as:

$$N_{AUX} \ge \frac{1.5V \cdot N_{BOOST}}{V_{OUT} - \sqrt{2}V_{LINE,MAX}} = \frac{1.5 \cdot 34}{400 - \sqrt{2} \cdot 265} = 2.02[Turns]$$

Choice should be around 4~5 turns after adding 2~3 turns.

| 3. Inductor Auxiliary Winding Design                 |              |                   |  |  |

|------------------------------------------------------|--------------|-------------------|--|--|

| Minimum Aux Winding Turns (N <sub>AUX,MIN</sub> )    | 3            | Turns             |  |  |

| User Choice of Aux Winding Turns (N <sub>AUX</sub> ) | 5            | Turns             |  |  |

| Winding Diameter                                     | 0.10         | mm                |  |  |

| Maximum Current Density of Coil                      | <u>1.273</u> | A/mm <sup>2</sup> |  |  |

|                                                      |              |                   |  |  |

#### [STEP-4] ZCD Circuit Design

If a transition time when  $V_{AUXII,IARY}$  drops from 1.4V to 0V is ignored from Figure 15, the needed additional delay by the external resistor and capacitor is one quarter of the resonant period. The time constant made by ZCD resistor and capacitor should be the same as one quarter of the resonant period:

$$R_{ZCD} \cdot C_{ZCD} = \frac{2\pi\sqrt{C_{\text{eff}} \cdot L}}{4} \tag{12}$$

where  $C_{\text{eff}}$  is the effective capacitor shown at the MOSFET drain pin;  $C_{ZCD}$  is the external capacitance at the ZCD pin; and  $R_{ZCD}$  is the external resistance at the ZCD pin.

The second role of  $R_{ZCD}$  is the current limit of the internal negative clamp circuit when auxiliary voltage drops to negative due to MOSFET turn on. ZCD voltage is clamped 0.65V and minimum  $R_{ZCD}$  can be given as:

$$R_{ZCD} \ge \frac{\left(\frac{N_{AUX}}{N_{BOOST}} \sqrt{2} V_{LINE,MAX} - 0.65V\right)}{3mA} [\Omega]$$

(13)

where 3mA is the clamping capability of the ZCD pin.

The calculation result of Equation (13) is normally higher than 15k $\Omega$ . If 20k $\Omega$  is assumed as R<sub>ZCD</sub>, calculated C<sub>ZCD</sub> from Equation (12) is around 10pF when the other components are assumed as conventional values used in the field. Because most IC pins have several pF parasitic capacitance, C<sub>ZCD</sub> can be eliminated when R<sub>ZCD</sub> is higher

than  $30k\Omega$ . However, a small capacitor would be helpful when auxiliary winding suffers from operating noise.

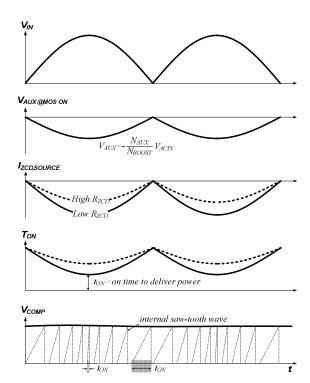

The PFC control loop has two conflicting goals: output voltage regulation and making the input current shape the same as input voltage. If the control loop reacts to regulate output voltage smoothly, as shown in Figure 16, control voltage varies widely with the input voltage variation. Input current acts to the control loop and sinusoidal input current shape can not be attained. This is the reason control response of most PFC topologies is very slow and turn-on time over AC period is kept constant. This is also the reason output voltage ripple is made by input and output power relationship, not by control-loop performance.

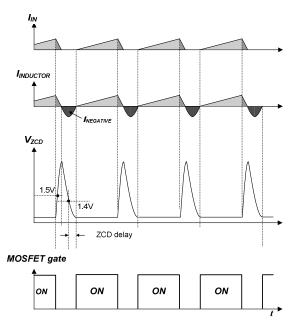

Figure 16. Input Current Deterioration by Fast Control

If on-time is controlled constantly over one AC period. inductor current peak follows AC input voltage shape and achieves good power factor. Off-time is basically inductor current reset time due to the boundary mode and is determined by the input and output voltage difference. When input voltage is at its peak, the voltage difference between input and output voltage is small, and long turnoff time is necessary. When input voltage is near zero, turn-off time is short, as shown in Figure 17 and Figure 18. Though inductor current drops to zero, there is a minor delay, explained above. The delay can be assumed as fixed when AC is at line peak and zero. Near AC line peak, the inductor current decreasing slope is slow and inductor current slope is also slow during the ZCD delay. The amount of negative current is not much higher than the inductor current peak. Near the AC line zero, inductor current decreasing slope is very high and the amount of negative current is higher than positive inductor current peak because input voltage is almost zero.

Figure 17. Inductor Current at AC Voltage Peak

Figure 18. Inductor Current at AC Voltage Zero

Negative inductor current creates zero current distortion and degrades the power factor. Improve this by extending turn-on time at the AC line input near the zero cross.

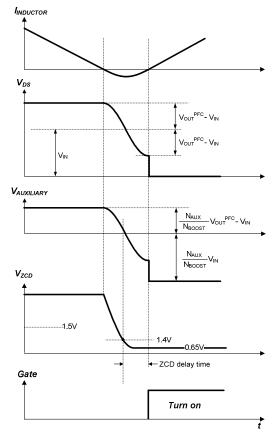

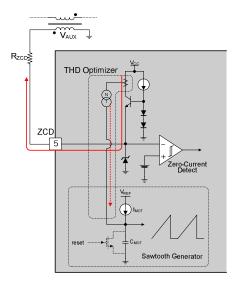

Negative auxiliary winding voltage, when MOSFET is turned on, is linearly proportional to the input voltage. Sourcing current generated by the internal negative clamping circuit is also proportional to sinusoidal input voltage. That current is detected internally and added to the internal sawtooth generator, as shown in Figure 19.

Figure 19. ZCD Current and Sawtooth Generator

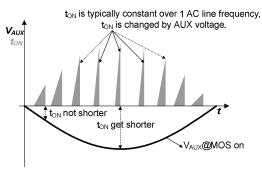

When AC input voltage is almost zero, no negative current is generated from inside, but sourcing current when input voltage is high is used to raise the sawtooth generator slope and turn-on time is shorter. As a result, turn-on time when AC voltage is zero is longer compared to AC voltage, in peaks shown in Figure 20.

Figure 20. THD Improvement

The current that comes from the ZCD pin, when auxiliary voltage is negative, depends on  $R_{\rm ZCD}$ . The second role of  $R_{\rm ZCD}$  is also related with the improving the Total Harmonic Distortion (THD).

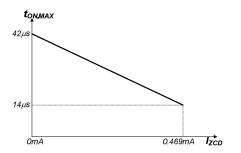

The third role of  $R_{ZCD}$  is making the maximum turn-on time adjustment. Depending on sourcing current from the ZCD pin, the maximum on-time varies as in Figure 21.

Figure 21. Maximum On-Time Variation vs. Izcd

With the aid of  $I_{ZCD}$ , an internal sawtooth generator slope is changed and turn-on time varies as shown in Figure 22.

Figure 22. Internal Sawtooth Wave Slope Variation

$R_{ZCD}$  also influences control range. Because FAN7930 doesn't detect input voltage, voltage-mode control value is determined by the turn-on time to deliver needed current to boost output voltage. When input voltage increases, control voltage decreases rapidly. For example, if input voltage doubles, control voltage drops to one quarter. Making control voltage maximum when input voltage is low and at full load is necessary to use the whole control range for the rest of the input voltage conditions. Matching maximum turn-on time needed at low line is calculated in Equation (7) and turn-on time adjustment by  $R_{ZCD}$  guarantees use of the full control range.  $R_{ZCD}$  for control range optimization is obtained as:

$$R_{ZCD} \ge \frac{28\mu s}{t_{ON,MAX1} - t_{ON,MAX}} \cdot \frac{\sqrt{2} \cdot V_{LINE,MIN} \cdot N_{AUX}}{0.469 mA \cdot N_{BOOST}}$$

(14)

where

$t_{ON,MAX}$  is calculated by Equation (7);  $t_{ON,MAXI}$  is maximum on-time programming 1;  $N_{BOOST}$  is the winding turns of boost inductor; and  $N_{AUX}$  is the auxiliary winding turns.

$R_{ZCD}$  calculated by Equation (13) is normally lower than the value calculated in Equation (14). To guarantee the needed turn on-time for the boost inductor to deliver rated power, the resulting  $R_{ZCD}$  from Equation (13) is normally not suitable.  $R_{ZCD}$  should be higher than the result of Equation (14) when output voltage drops as a result of low line voltage.

When input voltage is high and load is light, not much input current is needed and control voltage of  $V_{COMP}$  touches switching stop level, such as if FAN7930 is 1V. However, in some applications, a PFC block is needed to operate normally at light load. To compensate control

range correctly, input voltage sensing is necessary, such as with Fairchild's interleaved PFC controller FAN9612, or special care on sawtooth generator is necessary. Without it, optimizing  $R_{\rm ZCD}$  is only slightly helpful for control range. This is explained and depicted in the associated  ${\rm Excel}^{\circledast}$  design tool "COMP Range" worksheet. To guarantee enough control range at high line, clamping output voltage lower than rated output on the minimum input condition can help.

(Design Example) Minimum  $R_{ZCD}$  for clamping capability is calculated as:

$$R_{ZCD} \ge \frac{\left(\frac{N_{AUX}}{N_{BOOST}}\sqrt{2}V_{LINE,MAX} - 0.65V\right)}{3mA}$$

$$= \frac{\left(\frac{5}{34}\sqrt{2} \cdot 265 - 0.65V\right)}{3mA} = 18.2k\Omega$$

Minimum  $R_{\text{ZCD}}$  for control range is calculated as:

$$\begin{split} R_{ZCD} &\geq \frac{28 \mu s}{t_{ON,MAX1} - t_{ON,MAX}} \cdot \frac{\sqrt{2} \cdot V_{LINE,MIN} \cdot N_{AUX}}{0.469 mA \cdot N_{BOOST}} \\ &= \frac{28 \mu s}{42 \mu s - 10.9 \mu s} \cdot \frac{\sqrt{2} \cdot 90 \cdot 5}{0.469 mA \cdot 34} = 37.2 k\Omega \end{split}$$

A choice close to the value calculated by the control range is recommended.  $39k\Omega$  is chosen in this case.

| Minimum Value for R <sub>ZCD</sub> for THD Improvement |                      |              | k  |

|--------------------------------------------------------|----------------------|--------------|----|

| Minimum Value for R <sub>ZCD</sub> for Control         | Range                | 37.2         | k  |

| User Choice of R <sub>ZCD</sub>                        |                      | 39.0         | k  |

| R <sub>ZCD</sub> is also related with COMP (co         | ntrol voltage) range | e.           |    |

| Please refer to the "COMP range" w                     | nrksheet to select   | Race entimal | Ιν |

#### [STEP-5] Output Capacitor Selection

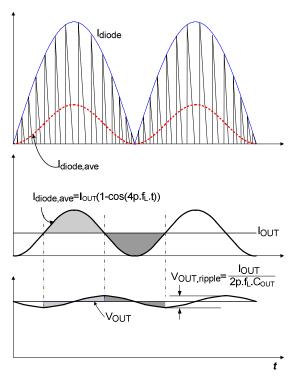

The output voltage ripple should be considered when selecting the output capacitor. Figure 23 shows the line frequency ripple on the output voltage. With a given specification of output ripple, the condition for the output capacitor is obtained as:

$$C_{OUT} \ge \frac{I_{OUT}}{2\pi \cdot f_{LINE} \cdot \Delta V_{OUT,RIPPLE}} [F]$$

(15)

where  $V_{\text{OUT,RIPPLE}}$  is the peak-to-peak output voltage ripple specification.

The output voltage ripple caused by ESR of electrolytic capacitor is not as serious as other power converters because output voltage is high and load current is small. Since too much ripple on the output voltage may cause premature OVP during normal operation, the peak-to-peak ripple specification should be smaller than 15% of the nominal output voltage.

The hold-up time should also be considered when determining the output capacitor as:

$$C_{OUT} \ge \frac{2 \cdot P_{OUT} \cdot t_{HOLD}}{\left(V_{OUT} - 0.5 \cdot \Delta V_{OUT,RIPPLE}\right)^2 - V_{OUT,MIN}^2} [f]$$

(16)

where  $t_{HOLD}$  is the required hold-up time and  $V_{OUT,MIN}$  is the minimum output voltage during hold-up time.

Figure 23. Output Voltage Ripple

The voltage rating of capacitor can be obtained as:

$$V_{ST,COUT} = \frac{V_{OVP,MAX}}{V_{REF}} \cdot V_{OUT}[V]$$

(17)

where  $V_{\text{OVP,MAX}}$  and  $V_{\text{REF}}$  are the maximum tolerance specifications of over-voltage protection triggering voltage and reference voltage at error amplifier.

(**Design Example**) With the ripple specification of 8V<sub>p-p</sub>, the capacitor should be:

$$C_{\rm O} \ge \frac{I_{\rm OUT}}{2\pi \cdot f_{\rm LINE} \cdot \Delta V_{\rm OUT, ripple}} = \frac{0.5}{2\pi \cdot 50 \cdot 8} = 198.9 [\,\mu F\,]$$

Since minimum allowable output voltage during one cycle line (20ms) drop-outs is 330V, the capacitor should be:

$$C_{O} \ge \frac{P_{OUT} \cdot t_{HOLD}}{\left(V_{OUT} - 0.5 \cdot \Delta V_{OUT, ripple}\right)^{2} - V_{OUT, MIN}^{2}}$$

$$= \frac{2 \cdot 200 \cdot 20 \times 10^{-3}}{\left(400 - 0.5 \cdot 8\right)^{2} - 330^{2}} = 167[\mu F]$$

To meet both conditions, the output capacitor must be larger than 199μF. A 220μF capacitor is selected for the output capacitor.

The voltage stress of selected capacitor is calculated as:

$$V_{ST,COUT} = \frac{V_{OVP,MAX}}{V_{REF}} \cdot V_{OUT} = \frac{2.730}{2.500} \cdot 400 = 4368[V]$$

| Maximum Allowable Output Voltage Ripple             | 8.0          | V  |

|-----------------------------------------------------|--------------|----|

| Minimum Out Capacitance                             | <u>198.9</u> | μF |

| Needed Holdup Time                                  | 20.0         | ms |

| Minimum Allowable Operating Voltage During Holdup   | 330.0        | V  |

| Minimum Output Capacitance Considering Holdup Time  | <u>167.0</u> | μF |

| To meet both minimum conditions, select bigger one. |              | ~  |

| Otherwise select proper one to meet system spec.    |              |    |

| Maximum Voltage Stress                              | <u>436.8</u> | V  |

| Recommended Output Capacitance                      | <u>198.9</u> | μF |

| User Choice of Output Capacitance                   | 220 00       | цF |

#### [STEP-6] MOSFET and DIODE Selection

Selecting the MOSFET and diode needs extensive knowledge and calculation regarding loss mechanisms and gets more complicated if proper selection of a heatsink is added. Sometimes the loss calculation itself is based on assumptions that may be far from reality. Refer to industry resources regarding these topics. This note shows the voltage rating and switching loss calculations based on the linear approximation.

The voltage stress of the MOSFET is obtained as:

$$V_{ST,Q} = \frac{V_{OVP,MAX}}{V_{REF}} \cdot V_{OUT} + V_{DROP,DOUT} [V]$$

(18)

where  $V_{\text{DROP},\text{DOUT}}$  is the maximum forward-voltage drop of output diode.

After the MOSFET is turned off, the output diode turns on and a large output electrolytic capacitor is shown at the drain pin, thus a drain voltage clamping circuit that is necessary on other topologies is not necessary in PFC. During the turn-off transient, boost inductor current changes the path from MOSFET to output diode and before the output diode turns on; a minor voltage peak can be shown at drain pin, which is proportional to MOSFET turn-off speed.

MOSFET loss can be divided into three parts: conduction loss, turn-off loss, and discharge loss. Boundary mode guarantees ZCS (Zero Current Switching) of MOSFET when turned on, so turn-on loss is negligible.

The MOSFET RMS current and conduction loss are obtained as:

$$I_{Q,RMS} = I_{L,PK} \cdot \sqrt{\frac{1}{6} - \frac{4\sqrt{2} \cdot V_{LINE}}{9\pi \cdot V_{QUT}}} [A]$$

(19)

$$P_{Q,CON} = (I_{Q,RMS})^2 \cdot R_{DS,ON} [W]$$

(20)

where  $I_{Q,RMS}$  is the RMS value of MOSFET current,  $P_{Q,CON}$  is the conduction loss caused by MOSFET current, and  $R_{DS,ON}$  is the ON resistance of the MOSFET.

ON resistance is described as "static ON resistance" and varies depending on junction temperature. That variation information is normally supplied as a graph in the datasheet and may vary by manufacturer. When calculating conduction loss, generally multiply three with the  $R_{\rm DS,ON}$  for more accurate estimation.

The precise turn-off loss calculation is difficult because of the nonlinear characteristics of MOSFET turn off. When piecewise linear current and voltage of MOSFET during turn-off and inductive load are assumed, MOSFET turnoff loss is obtained as:

$$P_{Q,SWOFF} = \frac{1}{2} \cdot V_{OUT} \cdot I_L \cdot t_{OFF} \cdot f_{SW} [W]$$

(21)

where  $t_{OFF}$  is the turn-off time and  $f_{SW}$  is the switching frequency.

Boundary mode PFC inductor current and switching frequency vary at every switching moment. RMS inductor current and average switching frequency over one AC period can be used instead of instantaneous values.

Individual loss portions are changed according to the input voltage; maximum conduction loss appears at low line because of high input current; and maximum switching off loss appears at high line because of the high switching frequency. Thus, resulting loss is always lower than the summation of the two losses calculated above.

Capacitive discharge loss made by effective capacitance shown at drain and source, which includes MOSFET  $C_{OSS}$ , an externally added capacitor to reduce dv/dt and parasitic capacitors shown at drain pin, is also dissipated at MOSFET. That loss is calculated as:

$$P_{Q,DISCHG} = \frac{1}{2} (C_{OSS} + C_{EXT} + C_{PAR}) \cdot V_{OUT}^2 \cdot f_{SW} [W]$$

(22)

where

Coss is the output capacitance of MOSFET;

$C_{\mathrm{EXT}}$  is an externally added capacitor at drain and source of MOSFET; and

C<sub>PAR</sub> is the parasitic capacitance shown at drain pin.

Because the  $C_{OSS}$  is a function of the drain and source voltage, it is necessary to refer to graph data showing the relationship between  $C_{OSS}$  and voltage.

Estimate the total power dissipation of MOSFET as the sum of three losses:

$$P_{Q} = P_{Q,CON} + P_{Q,SWOFF} + P_{Q,DISCHG}[W]$$

(23)

Diode voltage stress is the same as the output capacitor stress calculated in Equation (17).

The average diode current and power loss are obtained as:

$$I_{DOUT,AVE} = \frac{I_{OUT}}{\eta} [A]$$

(24)

$$P_{DOUT} = V_{DROP,DOUT} \cdot I_{DOUT,AVE} \quad [W]$$

(25)

where  $V_{\mbox{\scriptsize DROP},\mbox{\scriptsize DOUT}}$  is the forward voltage drop of diode.

(Design Example) Internal reference at the feedback pin is 2.5V and maximum tolerance of OVP trigger voltage is 2.730V. If Fairchild's FCPF20N60 MOSFET and FFPF08H60S diode are selected,  $V_{D,FOR}$  is 2.1V at 8A, 25°C, maximum  $R_{DS,ON}$  is 0.19 $\Omega$  at drain current is 10A, and maximum  $C_{OSS}$  is 85pF at drain-source voltage is 480V.

$$V_{ST,Q} = \frac{V_{OVP,MAX}}{V_{REF}} \cdot V_{OUT} + V_{DROP,DIODE}$$

$$= \frac{2.73}{2.50} \cdot 400 + 2.1 = 4389 [V]$$

$$P_{Q,CON} = \left(I_{L,PK} \cdot \sqrt{\frac{1}{6} - \frac{4\sqrt{2} \cdot V_{LINE}}{9\pi \cdot V_{OUT}}}\right)^{2} \cdot \left(R_{DS,ON}\right)$$

$$= \left(6.984 \cdot \sqrt{\frac{1}{6} - \frac{4\sqrt{2} \cdot 90}{9\pi \cdot 400}}\right)^{2} \cdot (0.19 \times 3) = 3.38[W]$$

$$P_{Q,SWOFF} = \frac{1}{2} \cdot V_{OUT} \cdot I_L \cdot t_{OFF} \cdot f_{SW}$$

=  $\frac{1}{2} \cdot 400 \cdot 2.469 \cdot 50 \text{ns} \cdot 50 \text{k} / 2 = 1.54 [W]$

$$P_{Q,DISCHG} = \frac{1}{2} \cdot (C_{OSS} + C_{EXT} + C_{PAR}) \cdot V_{OUT}^2 \cdot f_{SW}$$

$$= \frac{1}{2} \cdot 85p \cdot 400^2 \cdot 50k/2 = 0.43 [W]$$

Diode average current and forward-voltage drop loss as:

$$I_{DOUT,AVE} = \frac{I_{OUT}}{\eta} = \frac{0.5}{0.9} = 0.56[A]$$

$P_{DOUT,LOSS} = V_{DOUT,FOR} \cdot I_{DOUT,AVE} = 2.1 \cdot 0.56 = 1.46[W]$

| Reference Voltage for Feedback          | 2.50          | V  |

|-----------------------------------------|---------------|----|

| Maximum OVP Level Considering Tolerance | 2.73          | V  |

| Maximum Voltage Stress on MOSFET        | <u>438.90</u> | V  |

| Maximum RMS Current on MOSFET           | 2.436         | A  |

| R <sub>DS(ON)</sub> of Selected MOSFET  | 0.19          | Ω  |

| C <sub>OSS</sub> of Selected MOSFET     | 85.0          | рF |

| Maximum Conduction Loss                 | 3.38          | W  |

| MOSFET Turn Off Loss                    | <u>1.54</u>   | W  |

| Discharge Loss                          | 0.43          | W  |

| Total MOSFET Loss                       | <u>5.35</u>   | W  |

| Output Diode selection                  |               |    |

| Maximum Reverse Voltage Stress          | <u>436.80</u> | V  |

| Average Current of Output Diode         | <u>0.56</u>   | A  |

| Forward Voltage Drop of Selected Diode  | 2.1           | V  |

| Estimated Diode Loss                    | 1.46          | W  |

#### [STEP-8] Determine Current-Sense Resistor

It is typical to set pulse-by-pulse current limit level a little higher than the maximum inductor current calculated by Equation (3). For 10% margin, the current-sensing resistor is selected as:

$$R_{\rm CS} = \frac{V_{\rm CS,LIM}}{I_{\rm L,PK} \cdot 1.1} \left[ \Omega \right] \tag{26}$$

Once resistance is calculated, its power loss at low line is calculated as:

$$P_{RCS} = I_{Q,RMS}^2 \cdot R_{CS} [W]$$

(27)

Power rating of the sensing resistor is recommended a twice the power rating calculated in Equation (27).

(**Design Example**) Maximum inductor current is 6.984A and sensing resistor is calculated as:

$$R_{\text{CS}} = \frac{V_{\text{CS,LIM}}}{I_{\text{ind}}^{\text{pk}} \cdot 1.1} = \frac{0.8}{6.984 \cdot 1.1} = 0.104[\Omega]$$

Choosing  $0.1\Omega$  as  $R_{\text{CS}}$ , power loss is calculated as:

$$P_{RCSLOSS} = I_{Q,RMS}^2 \cdot R_{CS} = 2.436^2 \cdot 0.1 = 0.59[W]$$

Recommended power rating of sensing resistor is 1.19W.

|   | 3. Determine Current Sensing Resistor        |                |

|---|----------------------------------------------|----------------|

|   | Current Sense Input Threshold Voltage Limit  | 0.80 V         |

|   | Maximum Value for R <sub>CS</sub>            | <u>0.104</u> Ω |

|   | User Choice of R <sub>CS</sub>               | 0.100 Ω        |

| ľ | Maximum Power Loss at R <sub>CS</sub>        | <u>0.59</u> W  |

|   | Recommended Power Rating for R <sub>CS</sub> | <u>1.19</u> W  |

#### [STEP-9] Design Compensation Network

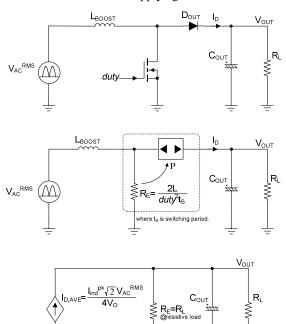

The boost PFC power stage can be modeled as shown in Figure 24. MOSFET and diode can be changed to loss-free resistor model and then be modeled as a voltage-controlled current source supplying RC network.

Figure 24. Small Signal Modeling of the Power Stage

By averaging the diode current during the half line cycle, the low-frequency behavior of the voltage controlled current source of Figure 24 is obtained as:

$$I_{DOUT,AVE} = K_{SAW} \cdot \frac{\sqrt{2}V_{LINE}}{4V_{OUT}} \cdot \frac{\sqrt{2}V_{LINE}}{L} [A]$$

(28)

where:

L is the boost inductance,

V<sub>OUT</sub> is the output voltage; and

$K_{SAW}$  is the internal gain of sawtooth generator (that of FAN7930 is  $8.496 \times 10^{-6}$ ).

Then the low-frequency, small-signal, control-to-output transfer function is obtained as:

$$\frac{\hat{V}_{OUT}}{\hat{V}_{COMP}} = K_{SAW} \cdot \frac{(V_{LINE})^2 R_L}{4V_{OUT} \cdot L} \cdot \frac{1}{1 + \frac{s}{2\pi f_p}}$$

(29)

where  $f_p = \frac{2}{2\pi \cdot R_L C_{OUT}}$  and  $R_L$  is the output load

resistance in a given load condition.

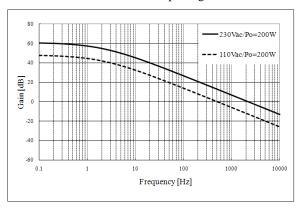

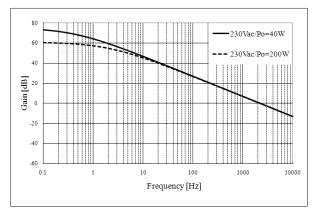

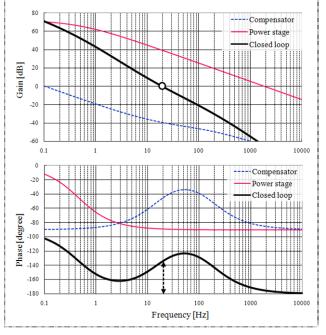

Figure 25 and Figure 26 show the variation of the control-to-output transfer function for different input voltages and different loads. Since DC gain and crossover frequency increase as input voltage increases, and DC gain increases as load decreases, high input voltage and light load is the worst condition for feedback loop design.

Figure 25. Control-to-Output Transfer Function for Different Input Voltages

Figure 26. Control-to-Output Transfer Function for Different Loads

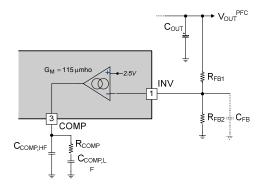

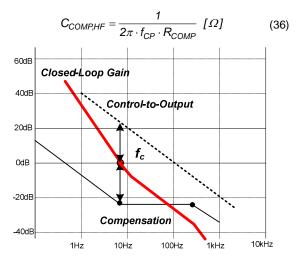

Proportional and integration (PI) control with high-frequency pole is typically used for compensation, as shown in Figure 27. The compensation zero ( $f_{CZ}$ ) introduces phase boost, while the high-frequency compensation pole ( $f_{CP}$ ) attenuates the switching ripple.

The transfer function of the compensation network is obtained as:

atput

$$\frac{\frac{1}{V_{COMP}}}{\frac{1}{V_{OUT}}} = \frac{2\pi f_I}{s} \cdot \frac{1 + \frac{s}{2\pi f_{CZ}}}{1 + \frac{s}{2\pi f_{CZ}}}$$

$$f_I = \frac{2.5}{V_{OUT}} \cdot \frac{115\mu mho}{2\pi \cdot (C_{COMP, LF} + C_{COMP, HF})}$$

(29) where  $f_{CZ} = \frac{1}{2\pi \cdot R_{COMP} \cdot C_{COMP, LF}}$

load

$$f_{CP} = \frac{1}{2\pi \cdot R_{COMP} \cdot \left(\frac{C_{COMP, LF} \cdot C_{COMP, HF}}{C_{COMP, LF} + C_{COMP, HF}}\right)}$$

where  $f_{CP} = \frac{1}{2\pi \cdot R_{COMP} \cdot \left(\frac{C_{COMP, LF} \cdot C_{COMP, HF}}{C_{COMP, LF} + C_{COMP, HF}}\right)}$

If  $C_{COMP,LF}$  is much larger than  $C_{COMP,HF}$ ,  $f_I$  and  $f_{CP}$  can be simplified as:

$$f_{I} \simeq \frac{2.5}{V_{OUT}} \cdot \frac{115\mu mho}{2\pi \cdot C_{COMP, LF}} [Hz]$$

$$f_{CP} \simeq \frac{1}{2\pi \cdot R_{COMP} \cdot C_{COMP, HF}} [Hz]$$

(31)

Figure 27. Compensation Network

The feedback resistor is chosen to scale down the output voltage to meet the internal reference voltage:

$$\frac{R_{FB1}}{R_{FB1} + R_{FB2}} \cdot V_{OUT} = 2.5V \tag{32}$$

Typically, high  $R_{\rm FB1}$  is used to reduce power consumption and, at the same time,  $C_{\rm FB}$  can be added to raise the noise immunity. The maximum  $C_{\rm FB}$  currently used is several nano farads. Adding a capacitor at the feedback loop introduces a pole as:

$$f_{FP} = \frac{1}{2\pi \cdot (R_{FB1} // R_{FB2}) \cdot C_{FB}}$$

$$\approx \frac{1}{2\pi \cdot R_{FB2} \cdot C_{FB}} [Hz]$$

(33)

where

$$(R_{FB1} // R_{FB2}) = \frac{R_{FB1} \cdot R_{FB2}}{R_{FB1} + R_{FB2}}$$

Though  $R_{FB1}$  is high, pole frequency made by the synthesized total resistance and several nano farads is several kilo hertz and rarely affects control-loop response.

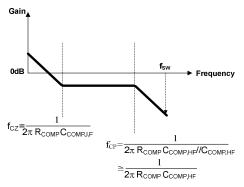

The procedure to design the feedback loop is:

a. Determine the crossover frequency (f<sub>C</sub>) around 1/10~1/5 of line frequency. Since the control-to-output transfer function of the power stage has -20dB/dec slope and -90° phase at the crossover frequency, as shown in Figure 28; it is required to place the zero of the compensation network (f<sub>CZ</sub>) around the crossover frequency so 45° phase margin is obtained. The capacitor C<sub>COMP,LF</sub> is determined as:

$$C_{COMP, LF} \cong \frac{K_{SAW}(V_{LINE})^2 2.5 \cdot 115 \mu \, mho}{2 \cdot V_{OUT}^2 \cdot L \cdot C_{OUT}(2\pi f_C)^2} [f]$$

(34)

To place the compensation zero at the crossover frequency, the compensation resistor is obtained as:

$$R_{COMP} = \frac{1}{2\pi \cdot f_C \cdot C_{COMP,LF}} \left[ \Omega \right]$$

(35)

b. Place this compensator high-frequency pole (f<sub>CP</sub>) at least a decade higher than f<sub>C</sub> to ensure that it does not interfere with the phase margin of the voltage regulation loop at its crossover frequency. It should also be sufficiently lower than the switching frequency of the converter for noise to be effectively attenuated. The capacitor C<sub>COMP,HF</sub> is determined as:

Figure 28. Compensation Network Design

(Design Example) If  $R_{FB1}$  is  $13M\Omega$ , then  $R_{FB2}$  is:

$$R_{FB2} = \frac{2.5V}{V_{OUT} - 2.5V} R_{FB1} = \frac{2.5}{400 - 2.5} 13 \times 10^6 = 81.7 k\Omega$$

Choosing the crossover frequency (control bandwidth) at 15Hz,  $C_{COMP,LF}$  is obtained as:

$$C_{COMP, LF} \approx \frac{K_{SAW}(V_{LINE})^2 2.5 \cdot 115 \mu mho}{2 \cdot V_{OUT}^2 \cdot L \cdot C_{OUT}(2\pi f_C)^2}$$

$$= \frac{8.496 \times 10^{-6} (230)^2 2.5 \cdot 115 \times 10^{-6}}{2 \cdot 400^2 \cdot 199 \times 10^{-6} \cdot 220 \times 10^{-6} (2\pi 15)^2} = 1038 nF$$

Actual  $C_{COMP,LF}$  is determined as 1000nF since it is the closest value among the off-the-shelf capacitors.  $R_{COMP}$  is obtained as:

$$R_{COMP} = \frac{1}{2\pi \cdot f_C \cdot C_{COMPLF}} = \frac{1}{2\pi \cdot 15 \cdot 1038 \times 10^{-9}} = 10.22k\Omega$$

Selecting the high-frequency pole as 150Hz,  $C_{\text{COMP,HF}}$  is obtained as:

$$C_{\text{COMP,HF}} = \frac{1}{2\pi \cdot f_{CP} \cdot R_{\text{COMP}}} = \frac{1}{2\pi \cdot 150 \cdot 10.22 \times 10^3} = 103nF$$

These components result in a control loop with a bandwidth of 19.7Hz and phase margin of 46°. The actual bandwidth is a little larger than the asymptotic design.

| Select R <sub>FB1</sub>                   |                   | 13.0           | M  |

|-------------------------------------------|-------------------|----------------|----|

| R <sub>FB2 r</sub> rs                     |                   | <u>81.76</u> k | ď  |

| Power Loss at Output S                    | Sensing Resistors | <u>12.23</u> n | n۷ |

| Transconductance of Error Amp             |                   | 115.0 կ        | ım |

| User Choice of Crossover Frequency        |                   | 15 I           | Ηz |

| Asymptotic Value for C <sub>COMP,LF</sub> |                   | 1036.51 n      | пF |

| Asymptotic Value for R <sub>COMP</sub>    |                   | 10.24 k        | ď  |

| Asymptotic Value for C <sub>COMP,HF</sub> |                   | 103.65 n       | пF |

| User Choice for C <sub>COMP.L</sub>       | LF.               | 1000.00 n      | пF |

| User Cchoice for R <sub>COMP</sub>        | )                 | 10.00 k        | ď  |

| User Choice for CCOMP I                   | 4F                |                | пF |

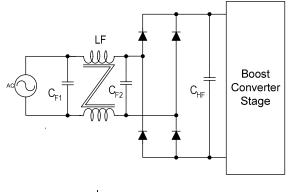

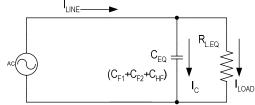

#### [STEP-10] Line Filter Capacitor Selection

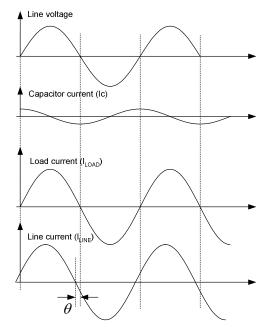

It is typical to use small bypass capacitors across the bridge rectifier output stage to filter the switching current ripple, as shown in Figure 29. Since the impedance of the line filter inductor at line frequency is negligible compared to the impedance of the capacitors, the line frequency behavior of the line filter stage can be modeled, as shown in Figure 29. Even though the bypass capacitors absorb switching ripple current, they also generate circulating capacitor current, which leads the line voltage by 90°, as shown in Figure 30. The circulating current through the capacitor is added to the load current and generates displacement between line voltage and current.

The displacement angle is given by:

$$\theta = \tan^{-1} \left( \frac{\eta \cdot (V_{LINE})^2 \cdot 2\pi \cdot f_{LINE} \cdot C_{EQ}}{P_{OUT}} \right)$$

(37)

where  $C_{EQ}$  is the equivalent capacitance that appears across the AC line ( $C_{EO}$ = $C_{F1}$ + $C_{F2}$ + $C_{HF}$ ).

The resultant displacement factor is:

$$DF = \cos(\theta) \tag{38}$$

Since the displacement factor is related to power factor, the capacitors in the line filter stage should be selected carefully. With a given minimum displacement factor ( $DF_{MIN}$ ) at full-load condition, the allowable effective input capacitance is obtained as:

$$C_{EA} < \frac{P_{OUT}}{\eta \cdot (V_{LINF})^2 \cdot 2\pi \cdot f_{LINF}} \cdot tan(\cos^{-1}(DF_{MN})) [F]$$

(39)

One way to determine if the input capacitor is too high or PFC control routine has problems is to check power factor (PF) and Total Harmonic Distortion (THD). PF is the degree to which input energy is effectively transferred to the load by the multiplication of displacement factor and THD that is input current shape deterioration ratio. PFC control loop rarely has no relation to displacement factor and input capacitor rarely has no impact on the input current shape. If PF is low (high is preferable), but THD is quite good (low is preferable), it can be concluded that input capacitance is too high and PFC controller is fine.

**(Design Example)** Assuming the minimum displacement factor at full load is 0.98, the equivalent input capacitance is obtained as:

$$\begin{split} &C_{EA} < \frac{P_{OUT}}{\eta \cdot \left(V_{LINE}\right)^2 \cdot 2\pi \cdot f_{LINE}} \cdot tar\left(cos^{-1}(DF_{MN})\right) \\ &< \frac{200}{0.9 \cdot \left(264\right)^2 \cdot 2\pi \cdot 50} \cdot tar\left(cos^{-1}(0.98)\right) = 2.0453 \mu F \end{split}$$

Thus, the sum of the capacitors on the input side should be smaller than  $2.0\mu F$ .

| 10. Line Filter Capacitor Selection                                           |        |    |

|-------------------------------------------------------------------------------|--------|----|

| Input Displacement Factor                                                     | 0.980  |    |

| Maximum Input Capacitance(C <sub>F1</sub> +C <sub>F2</sub> +C <sub>HF</sub> ) | 2.0453 | μF |

|                                                                               |        | 1  |

Figure 29. Equivalent Circuit of Line Filter Stage

Figure 30. Line Current Displacement

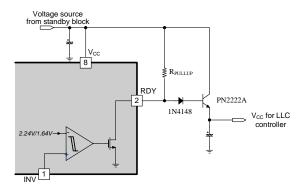

## Appendix 1: Use of the RDY Pin

Typically, boosted output voltage from the PFC block is used as input voltage to the DC-DC conversion block. For some types of DC-DC converter, it is recommended to trigger operation after the input voltage raised to some level. For example, LLC resonant converter or forward converter's input voltage is limited to some range to enhance performance or guarantee the stable operation.

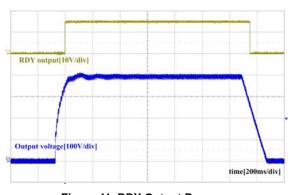

For that purpose, the PFC RDY pin is assigned and can be used as a acknowledge signal for the DC-DC conversion stages. When PFC output voltage rises higher than the internal threshold, PFC RDY output is pulled HIGH by the external pull-up voltage and drops to zero with hysteresis.

$$V_{OUT,RDYH} = \frac{2.240V}{2.500V} V_{OUT} [V]$$

$$V_{OUT,RDYL} = \frac{1.640V}{2.500V} V_{OUT} [V]$$

(40)

where  $V_{OUT,RDYH}$  is the  $V_{OUT}$  voltage to trigger PFC RDY output to pull HIGH and  $V_{OUT,RDYL}$  is the  $V_{OUT}$  voltage to trigger PFC ready output to drop to zero.

If rated  $V_{OUT}$  is  $400V_{DC}$ , then  $V_{OUT,RDYH}$  is  $358V_{DC}$ , and  $V_{OUT,RDYL}$  is  $262V_{DC}$ .

When LLC resonant converter is assumed to connect at the PFC output, the RDY pin can control the  $V_{\rm CC}$  for the LLC controller, as shown in Figure 31.

Figure 31. RDY Application Circuit for V<sub>CC</sub> Driving

$R_{\text{PULLUP}}$  is chosen based on the current capability of internal open-drain MOSFET and can be obtained as:

$$R_{PULLUP} \ge \frac{V_{PULLUP} - V_{RDY,SAT}}{I_{RDY,SK}} [\Omega]$$

(41)

where  $V_{PULLUP}$  is the pull-up voltage,  $V_{RDY,SAT}$  is the saturation voltage of the internal MOSFET, and  $I_{RDY,SK}$  is the allowable sink current for the internal MOSFET.

A fast diode, such as 1N4148, is needed to prohibit the emitter-base breakdown. Without that diode, when RDY voltage drops to  $V_{RDY,SAT}$  after being pulled up, emitter voltage maintains operating voltage for LLC controller and almost all the voltage is applied to the emitter and base. Breakdown current flows from emitter, base, and drain of the MOSFET to the source of MOSFET. Because a large electrolytic capacitor is typically used at the  $V_{CC}$

supply, that breakdown current flows high for a long time. In this case, the internal MOSFET may be damaged since the external small-signal bipolar junction transistor current capability is higher than the internal RDY MOSFET.

Once circuit configuration is settled, voltage after subtracting forward-voltage drop of the diode and voltage drop (by the multiplication of base current and  $R_{\rm PULLUP})$  from the  $V_{\rm CC}$  of FAN7930 is available for the LLC controller's  $V_{\rm CC}$  source.

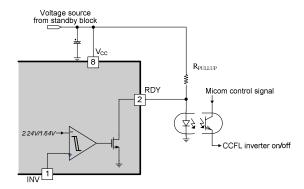

Another example is using RDY when the secondary side needs PFC voltage information. When a Cold Cathode Fluorescent Lamp (CCFL) is used for the backlight source of an LCD TV, the inverter stage to ignite CCFL can receive PFC output voltage directly. For that application, Figure 32 can be a suitable circuit configuration.

Figure 32. RDY Application Circuit Using Opto-Coupler

With this application circuit, the minimum  $R_{PULLUP}$  is given by Equation (42) and the maximum  $R_{PULLUP}$  is limited by sufficient current to guarantee stable operation of the opto-coupler. Assuming 1mA is the typical quantity to drive opto-coupler, the maximum  $R_{PULLUP}$  is:

$$R_{PULLUP} \le \frac{V_{PULLUP} - V_{OPTQF}}{1mA} [\Omega]$$

(42)

where  $V_{\text{OPTO},R}$  is the input forward-voltage drop of the opto-coupler.

It may possible that a secondary microcontroller has authority to give a trigger signal to the CCFL inverter controller; however, after combining the microcontroller signal and RDY signal from the primary-side, the inverter stage is triggered only when the two signals meet the requirements at the same time.

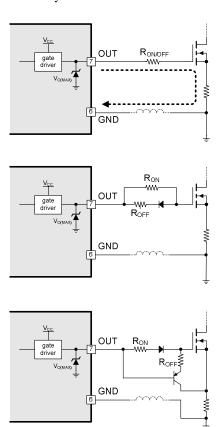

## **Appendix 2: Gate Driver Design**

FAN7930 directly drives the gate of the MOSFET and various combinations of gate driver circuits are possible. Figure 33Figure 31 shows the three circuits that are widely used.

When only one resistor is used, the turn-on and turn-off paths follow the same routine and turn-on and turn-off speed cannot be changed simultaneously. To cover this, make different paths by two resistors and diode if possible. Turn-off current flows through the diode first, instead of  $R_{\text{ON}}$ , and then  $R_{\text{ON}}$  and  $R_{\text{OFF}}$  show together. Accordingly, faster turn off is possible. However, turn-off path using internal gate driver's sinking path and current is limited by sinking current capability. If a PNP transistor is added between the gate and source of the MOSFET, the gate is shorted to source locally without sharing the current path to the gate driver. This makes the gate discharge to the much smaller path than that made by the controller. The possibility of ground bounce is reduced and power dissipation in the gate driver is reduced. Due to new high-speed MOSFET types such as SupreMOS® or SuperFET<sup>™</sup>, gate speed is getting fast. This decreases the switching loss of the MOSFET. At the same time, power systems suffer from the EMI deterioration or noise problems, like gate oscillation. Therefore, sometimes a gate discharge circuit is inevitable to use high-speed characteristics fully.

Figure 33. Equivalent Circuit of Line Filter Stage

The most difficult and uncertain task in direct gate drive is optimizing circuit layout. Gate driving path from the OUT pin, resistor, MOSFET gate, and MOSFET source to the GND pin should be as short as possible to reduce parasitic inductance; which may make MOSFET on/off speed slow or introduce unwanted gate oscillation. Using a wider PCB pattern for this lane reduces parasitic inductance. To damp unwanted gate oscillation made by the capacitance at the gate pin and parasitic inductance formed by MOSFET internal bonding wire and PCB pattern, proper resistance can match the impedance at the resonant frequency. To meet EMI regulations or for the redundant system, fast gate speed can be sacrificed by increasing serial resistance between the gate driver and gate.

An optimal gate driver circuit needs intensive knowledge of MOSFET turn-on/off characteristics and consideration of the other critical performance requirements of the system. This is beyond the scope of this paper and many reference papers can be found in the industry literature.

# **Appendix 3: Design Summary**

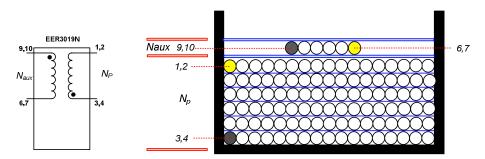

Figure 34 shows the schematic of the 200W BCM boost PFC design example used in this application note. EER3019N core is used for the boost inductor.

Figure 34. Schematic of Design Example

Figure 35. Boost Inductor Specification

Table 1. Winding Specification

|                 | Pin                                | Diameter / Thickness | Turns |

|-----------------|------------------------------------|----------------------|-------|

| NP              | IP 3,4 → 1,2 0.1φ x 50 (Litz wire) |                      | 34    |

| Insula          | ation Tape                         | 0.05mm               | 3     |

| NAUX            | 9,10 → 6,7                         | 0.3φ                 | 5     |

| Insulation Tape |                                    | 0.05mm               | 3     |

Core: EER3019N (Ae=137 mm<sup>2</sup>)

Bobbin: EER3019N Inductance: 210µH

# **Appendix 4. Experimental Verification**

To show the validity of the design procedure presented in this application note, the converter of the design example was built and tested. All the circuit components are exactly as designed in the example.

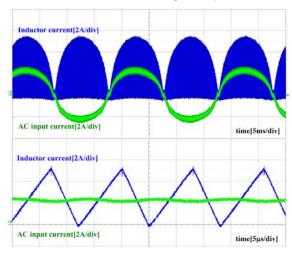

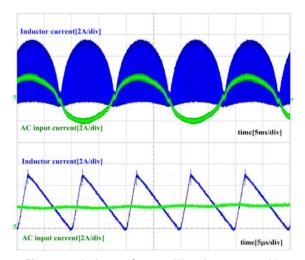

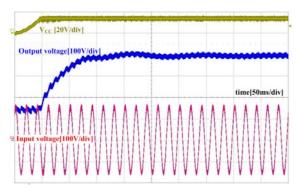

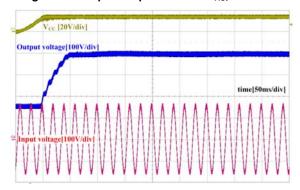

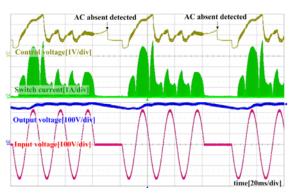

Figure 36 and Figure 37 show the inductor current and input current for  $115V_{AC}$  and  $230V_{AC}$  condition. Figure 38 and Figure 39 show the output response for  $115V_{AC}$  full-load and no-load conditions. Regardless of load conditions, output voltage shows no overshoot. Figure 39 shows response when AC input voltage was omitted 20ms periodically. As observed, control voltage was clamped when AC absent was detected internally and restarted smoothly when AC was applied again. Figure 41 shows RDY output response. The PFC performances are shown in Table 2. The power factor at full load is 0.992 and 0.990 for  $110V_{AC}$  and  $230V_{AC}$ , respectively.

Figure 36. Inductor Current Waveforms at 110V<sub>AC</sub>

Figure 37. Inductor Current Waveforms at 230 $V_{\text{AC}}$

Figure 38. Output Response at 110V<sub>AC</sub>, Full Load

Figure 39. Output Response at 110VAC, No Load

Figure 40. AC-Absent Detection Operation

Figure 41. RDY Output Response

Table 2. Performance Results

| V <sub>IN</sub>    | P <sub>OUT</sub> [W] | η [%] | PF    | THD [%] |

|--------------------|----------------------|-------|-------|---------|

|                    | 100                  | 95.5  | 0.996 | 8.52    |

| 85V <sub>AC</sub>  | 150                  | 94.4  | 0.995 | 10.21   |

|                    | 200                  | 93.4  | 0.994 | 11.11   |

|                    | 100                  | 96.5  | 0.995 | 8.26    |

| 115V <sub>AC</sub> | 150                  | 96.3  | 0.993 | 10.87   |

|                    | 200                  | 95.7  | 0.992 | 12.33   |

|                    | 100                  | 96.9  | 0.965 | 13.59   |

| 230V <sub>AC</sub> | 150                  | 97.6  | 0.985 | 4.83    |

|                    | 200                  | 97.9  | 0.990 | 7.57    |

|                    | 100                  | 97.1  | 0.939 | 19.99   |

| 264V <sub>AC</sub> | 150                  | 97.9  | 0.973 | 10.39   |

|                    | 200                  | 98.1  | 0.985 | 4.46    |

#### **Definition of Terms**

$\eta$  is the efficiency.

$\theta$  is the displacement angle.

$\Delta B$  is the maximum flux swing of the core at nominal output power in Tesla.

Ae is the cross-sectional area of core.

Aw is the window area of core.

B<sub>MAX</sub> is the maximum flux density of boost inductor at maximum output power in Tesla.

C<sub>COMP,HF</sub> is the high-frequency compensation capacitance.

C<sub>COMP,LF</sub> is the low-frequency compensation capacitance.

Ceff is the effective capacitance shown at the MOSFET drain pin.

C<sub>EA</sub> is the effective input capacitance to meet a given displacement factor.

$C_{\text{EXT}}$  is the external capacitance at drain-source to decrease the turn-off slope.

$C_{\text{EQ}}$  is the equivalent input capacitance.

$C_{FB}$  is the feedback capacitance parallel with  $R_{FB2}$ .

$C_{\text{OUT}}$  is the output capacitance.

C<sub>OSS</sub> is the output capacitance of power MOSFET.

$C_{\text{PAR}}$  is the parasitic capacitance at drain-source of power MOSFET.

C<sub>ZCD</sub> is the capacitance connected at ZCD pin to improve noise immunity.

$d_{\text{WIRE}}$  is the diameter of boost inductor winding wire.

DF is the displacement factor between input voltage and input current.

f<sub>C</sub> is the crossover frequency.

f<sub>CP</sub> is the high-frequency compensation pole to attenuate the switching ripple.

f<sub>CZ</sub> is the compensation zero.

$f_{LINE}$  is the line frequency.

f<sub>I</sub> is the integral gain of the compensator.

f<sub>P</sub> is the pole frequency in the PFC power stage transfer function.

f<sub>sw</sub> is the switching frequency.

f<sub>SW,MIN</sub> is the minimum switching frequency.

I<sub>CS,LIM</sub> is the pulse-by-pulse current limit level determined by sensing resistor.

I<sub>DOUT,AVE</sub> is the average current of output diode.

$I_{IN.MAX}$  is the maximum input current from the AC outlet.

I<sub>IN.MAXRMS</sub> is the maximum RMS (Root Mean Square) input current from the AC outlet.

I<sub>L</sub> is the inductor current at the nominal output power.

I<sub>L,PK</sub> is the maximum peak inductor current at the nominal output power.

I<sub>L.RMS</sub> is the RMS value of the inductor current at the nominal output power.

$I_{L,DENSITY}$  is the current density of the boost inductor coil.

$I_{\text{OUT}}$  is the nominal output current of the boost PFC stage.

I<sub>O,RMS</sub> is the RMS current at the power switch.

$I_{RDY,SK}$  is the allowable sink current for the internal MOSFET in RDY pin.

$K_{SAW}$  is the internal gain of sawtooth generator (that of FAN7930 is  $8.496 \times 10^{-6}$ ).

L is the boost inductance.

N<sub>AUX</sub> is the number of turns of auxiliary winding in boost inductor.

$N_{\mbox{\scriptsize BOOST}}$  is the number of turns of primary winding in boost inductor.

N<sub>WIRE</sub> is the number of strands of boost inductor winding wire.

P<sub>DOUT</sub> is the loss of output diode.

P<sub>OUT</sub> is the nominal output power of boost PFC stage.

P<sub>O.CON</sub> is conduction loss of the power MOSFET.

P<sub>O,SWOFF</sub> is turn-off loss of power MOSFET.

$P_{Q,DISCHRGE}$  is the drain-source capacitance discharge loss and consumed at power MOSFET.

P<sub>Q</sub> is the total loss of power MOSFET made by P<sub>Q,CON</sub>, P<sub>Q,SWOFF</sub>, and P<sub>Q,DISCHARGE</sub>.

P<sub>RCS</sub> is the power loss caused by current-sense resistance.

R<sub>COMP</sub> is the compensation resistance.

R<sub>CS</sub> is the power MOSFET current-sense resistance.

$R_{DS,ON}$  is the static drain-source on resistance of the power switch.

$R_{FB1}$  is the feedback resistance between the INV pin and output voltage.

R<sub>FB2</sub> is the feedback resistance between the INV pin and ground.

R<sub>L</sub> is the output load resistance in a given load condition.

$R_{\mbox{\scriptsize PULLUP}}$  is the pull-up resistance between the RDY pin and pull-up voltage.

$R_{ZCD}$  is the resistor connected at the ZCD pin to optimize THD.

$t_{HOLD}$  is the required hold-up time.

t<sub>OFF</sub> is the inductor current reset time.

t<sub>ON,MAX</sub> is the maximum on time fixed internally.

t<sub>ON.MAX1</sub> is the programmed maximum on time.

V<sub>COMP</sub> is compensation pin voltage.

V<sub>CS,LIM</sub> is power MOSFET current-sense limit voltage.

$V_{DROP,DOUT}$  is the forward-voltage drop of output diode.

V<sub>IN</sub>(t) is the rectified line voltage.

V<sub>IN,PK</sub> is the amplitude of line voltage.

V<sub>LINE</sub> is RMS line voltage.

$V_{\text{LINE,MAX}}$  is the maximum RMS line voltage.

V<sub>LINE,MIN</sub> is the minimum RMS line voltage.

V<sub>LINE,OVP</sub> is the line OVP trip point in RMS.

V<sub>OPTO,F</sub> is the input forward voltage drop of opto-coupler.

V<sub>OUT</sub> is the PFC output voltage.

V<sub>OUT,MIN</sub> is the allowable minimum output voltage during the hold-up time.

V<sub>OUT,RDYH</sub> is the V<sub>OUT</sub> to trigger PFC RDY out pulls high.

$V_{\text{OUT},\text{RDYL}}$  is the  $V_{\text{OUT}}$  to trigger PFC RDY out drops to zero.

$\Delta V_{OUT,RIPPLE}$  is the peak-to-peak output voltage ripple.

$V_{\text{PULLUP}}$  is the pull-up voltage for RDY pin.

V<sub>RDY,SAT</sub> is the internal saturation voltage of RDY pin.

V<sub>REF</sub> is the internal reference voltage for the feedback input.

V<sub>OVP,MAX</sub> is the maximum tolerance of Over-Voltage Protection specification

$V_{\text{ST,COUT}}$  is the voltage stress at the output capacitor.

V<sub>ST,O</sub> is the voltage stress at the power MOSFET.

#### References

- [1] Fairchild Datasheet FAN9612, Interleaved Dual BCM, PFC Controller

- [2] Fairchild Datasheet FAN7930 Critical Conduction Mode PFC Controller

- [3] Fairchild Application Note AN-6027, Design of Power Factor Correction Circuit Using FAN7530

- [4] Fairchild Application Note AN-6086, Design Consideration for Interleaved BCM PFC using FAN9612

- [5] Robert W. Erikson, Dragan Maksimovic, Fundamentals of Power Electronics, Second Edition, Kluwer Academic Publishers, 2001.

#### **Related Datasheets**

FAN7930 — Critical Conduction Mode PFC Controller

FAN9611 / FAN9612 — Interleaved Dual BCM PFC Controllers

1N/FDLL 914/A/B / 916/A/B / 4148 / 4448 Small Signal Diode

PN2222A/MMBT2222A/PZT2222A NPN General Purpose Amplifier

FCPF20N60 - 600V N-Channel MOSFET, SuperFET<sup>TM</sup>

FFPF08H60S — 8A, 600V Hyperfast Rectifier

#### **Author**

YoungBae Park, System and Application Engineer

#### **Important Notice**

DISCLAIMER

FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION, OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS.

LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR CORPORATION.

As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, or (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in significant injury to the user.

- A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.